신기했던 SHR/SHL의 Intel CPU Behavior

edx = 0x7c5e cl = 40 = 0x28

레지스터가 위와 같은 상황에서 shr edx, cl 를 실행하면 어떻게 될까, 0x7c5e >> 0x28 == 0 이어서 0이 될 줄 알았지만 아니였다.

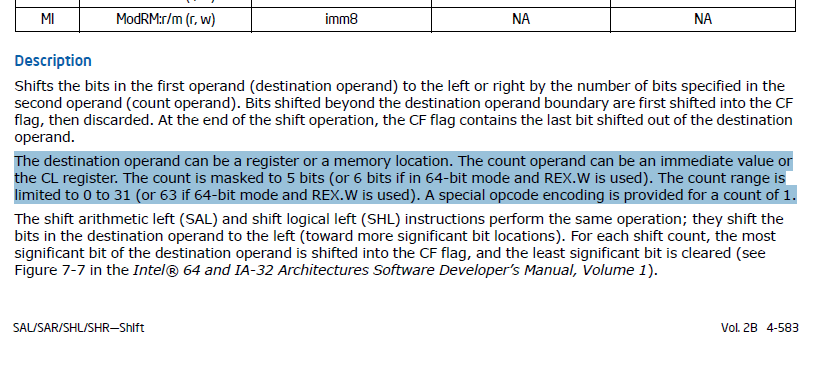

인텔 매뉴얼에서 SHR/SHL 어셈블리 파트(4-583)의 description을 읽어보면

이라고 되어있다. imm이나 cl이 오는 count operand에 0x1f를 마스킹한다고 한다. (따라서 32비트에서 count range는 0~31)

따라서 아까같은 상황에서는 0x28 & 0x1f == 0x8 이므로 연산결과는 0x7c이다.

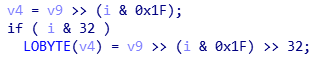

그래서 헥스레이에서 0x1f를 자동으로 붙여주고 32보다 더 쉬프트해야할때는 shrd, shr으로 처리한다

왜 이렇게 하는지 정확히 모르겠다. 예를들어 32비트에서 32 이상 shift는 무조건 0이니까 마스킹을 한다면 무언가 효율적인 연산을 생성할 수 있는 건가..

Recent Comments